박막 피에조 MEMS 파운드리

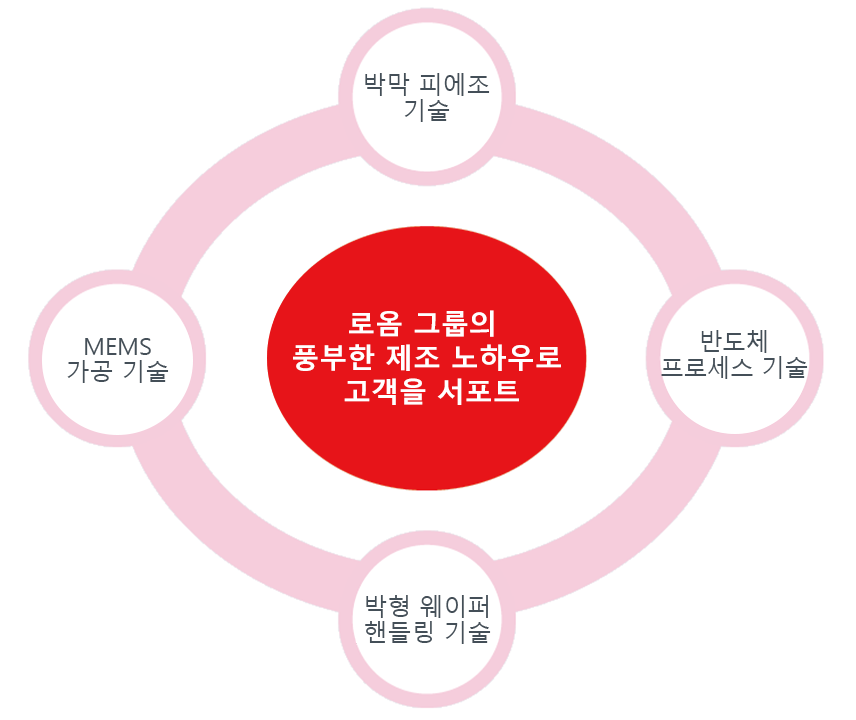

로옴은 강유전체가 지닌 많은 기술 혁신성에 주목하여, 오랫동안 연구 개발을 추진해왔습니다. 로옴의 박막 피에조 MEMS 파운드리는 그 기술과 이종 재료 매니지먼트 시스템의 경험을 살린 신뢰성과 안정성이 높은 독자적인 생산 장치를 통해, 박막 피에조와 LSI 미세 가공 기술을 융합시킬 수 있습니다. 고객과의 공동 개발을 통해 「지금까지 본적이 없고」「경험한 적도 없고」「상상할 수도 없었던」 저전력 · 소형 · 고기능 제품의 실현을 약속합니다.

피에조란? MEMS란? - 전자 기초 지식

피에조, MEMS의 기초 지식과 특징, 용도, 구조 및 특성에 대한 설명을 게재하고 있습니다.

개발 · 양산 위탁

주요 기술 · 서비스

실리콘 웨이퍼 및 SOI 웨이퍼 등을 사용한 MEMS 디바이스의 프로세스 계획 수립, 고성능 압전막 제조, 압전 MEMS 디바이스의 위탁 가공 및 설계 서포트 등, 프로토타입 제작에서 개발, 양산까지 토탈 서포트합니다. 홈페이지 및 카탈로그에 게재되어 있지 않은 개별 프로세스에 대한 상담도 별도 문의하여 주십시오.

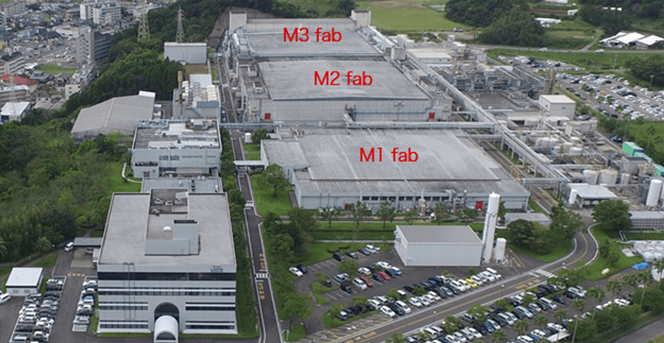

양산 · 개발 라인

라피스 세미컨덕터 미야자키 공장에 독자적인 박막 피에조 기술과 LSI 생산 라인을 융합한 6inch MEMS 라인을 구축하였습니다.

| 소재지 | Kiyotake-cho, Miyazaki City, Miyazaki Prefecture, Japan |

|---|---|

| 클린룸 | 피에조 MEMS 전용 공간 1,360m2 |

| 클린 레벨 | Class 1-1,000 |

| 웨이퍼 사이즈 | 6inch |

| 제공 서비스 | 개발 샘플 제작, 양산 |

| ISO 등 | ISO9001, ISO14001 |

| 개발 / 양산 경험 | 액추에이터, 센서 |

| 프로세스 기술 | PZT 압전 박막, 양면 Si 가공 가능, 웨이퍼 접합 |

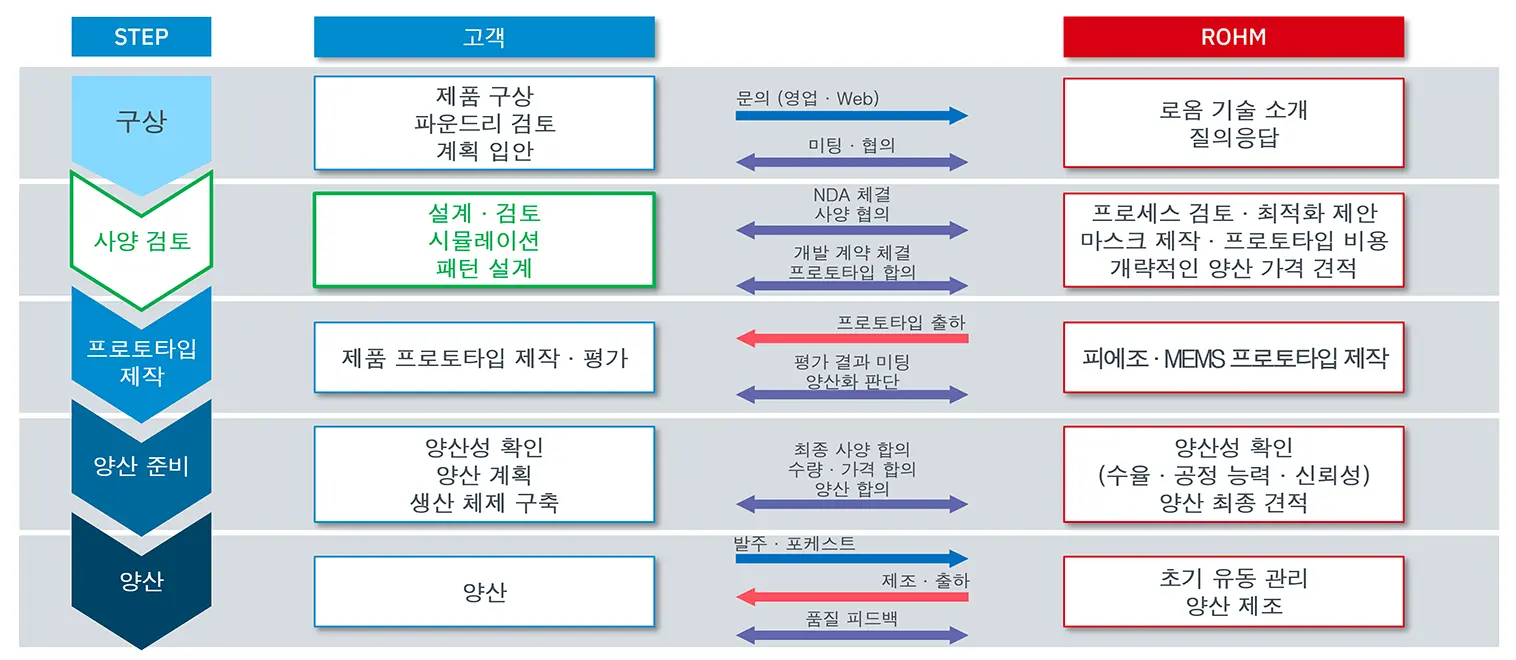

고객 상담에서 양산까지의 흐름

전용 MEMS 라인에서 파운드리 형식으로, 고객 제품의 프로토타입 제작부터 양산까지 대응하고 있습니다.

*상기 내용은 일반적인 예이며, 실제로는 안건에 따라 상담 후 결정하고 있습니다.

상담, 의뢰, 요청에 대해서는 하기 문의 양식을 통해 별도로 연락하여 주십시오.

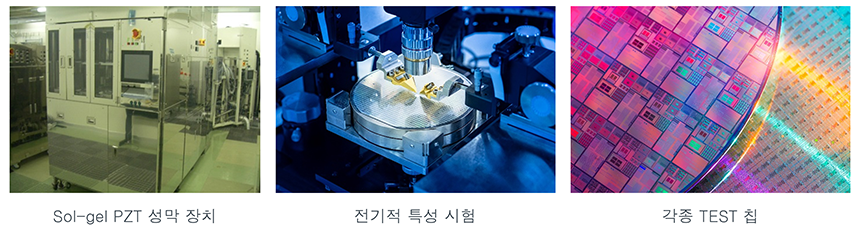

보유 설비

MEMS 프로세스에 필요한 설비, 해석 툴을 제조 라인 내에 보유함으로써, 폭넓은 디바이스의 프로세스 제안과 품질 향상이 가능합니다.

| 프로세스 분류 | 설비 |

|---|---|

| 성막 | |

| Sol-gel (PZT계) | |

| PE-CVD (SiO2, SiN) | |

| LP-CVD (SiO2, SiN, poly-Si) | |

| 열 산화로 | |

| 스퍼터 (Pt, Ir, IrO2, AlCu, Ti, TiN 등) | |

| ALD(Atomic Layer Deposition) (Al2O3, SiO2, Ta2O5) |

|

| 발수 코팅막 형성 | |

| 포토리소그래피 | |

| 도포 · 현상 | |

| MPA (Mirror Projection Aligner) | |

| 양면 얼라이너, IR 스테퍼, i선 스테퍼 | |

| 드라이 에칭 | |

| Si Deep RIE | |

| 층간막 RIE 장치 | |

| PZT · 전극용 ICP Etcher | |

| 웻 에칭 | |

| 실리콘 산화막 에칭 | |

| Au 에칭 | |

| Si 이방성 에칭 | |

| 웨이퍼 접합 | |

| 수지 접합 | |

| 양극 접합 |

| 프로세스 분류 | 설비 |

|---|---|

| 라미네이트 | |

| 웨이퍼 테이프 자동 라미네이팅 기계 (UV 테이프, 열 박리 시트, 폴리이미드 등) |

|

| 박리 · 세정 | |

| Asher | |

| 유기 · 폴리머 박리 | |

| 산 세정, 스크러버 | |

| 개편화 (個片化) 등 | |

| 다이싱, 2류체 세정 | |

| 서클 컷 다이서 | |

| 계측 관련 | |

| 해석 SEM · 측장 SEM, 이온 밀링 | |

| 광학식 측장 장치 | |

| 표리 정렬 불량 측정 장치 | |

| 가시광 · IR · 레이저 현미경 | |

| X선 회절 장치 | |

| 레이저식 변위 측정 장치 | |

| 형광 X선 분석 장치 | |

| 접침식 단차 측정기, 광학식 간섭 단차 측정기 | |

| 엘립소미터 | |

| 자동 외관 검사 장치 (표리 관통 웨이퍼 대응) | |

| 각종 전기적 특성 평가 장치 (프로브, 테스터) |

프로세스 능력

홈페이지 및 카탈로그에 게재되어 있지 않은 개별 프로세스에 대한 상담도 별도 문의하여 주십시오.

| 공정 | 프로세스 사양 | 수치 | 비고 |

|---|---|---|---|

| 포토리소그래피 | 최소 선폭 (스테퍼 사용) 최소 선폭 (얼라이너 사용) |

1μm 3μm |

|

| Si Deep RIE | 테이퍼 각도 에칭 비율 면내 균일성 치수 정밀도 |

90±1도 ≤5% ±0.1μm (모두 패턴에 의존) |

기판 관통 가공 가능 표리 양면 가공 가능 (Notch-free) 테이퍼 컨트롤 가능 |

| TMAH 에칭 | 깊이 | ≤면내 5% | 기판 관통 가공 가능 표리 양면 가공 가능 |

| PZT 성막 | 막 두께 정밀도 | 웨이퍼 내 ±1.0% 웨이퍼, lot 사이 ±2.5% |

도핑 예 (Nb, La) |

| PZT 에칭 | 가공 선폭 정밀도 에칭 비율 면내 균일성 |

±1μm ≤5% (PZT 두께 ~3μm, 테이퍼 형상 있음) |

Pt 스톱 가능 |

| 스퍼터 | 막 두께 균일성 | ≤면내 4% | Pt, Ir, IrO2, AlCu, Ti, TiN 등 |

| CVD | 막 두께 균일성 | ≤면내 4% | SiO2、SiN |

| ALD | 막 두께 균일성 | ≤면내 5% | Al2O3, Ta2O5, SiO2 |

| 수지 접합 | 얼라인먼트 정밀도 수지 두께 |

±5μm 1~3μm |

에폭시, BCB |

| 양극 접합 | 몰딩 내부 압력 | >0.01Pa | Si / 글래스 |

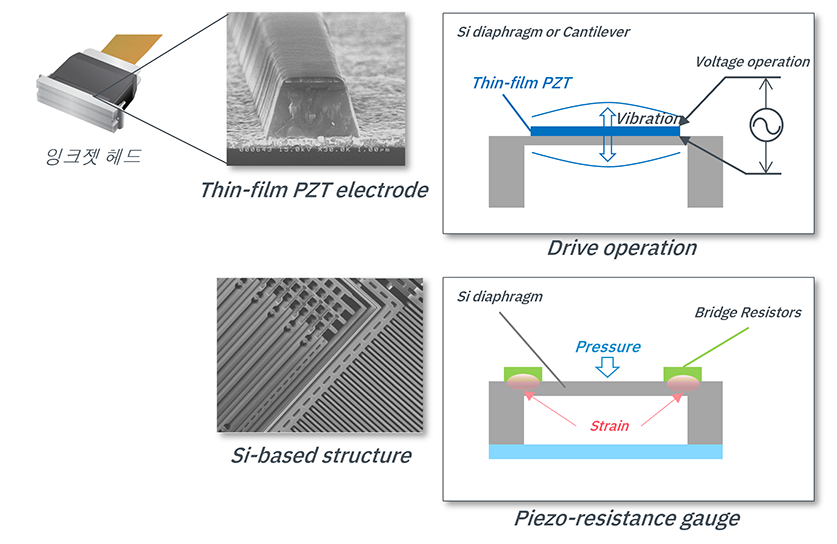

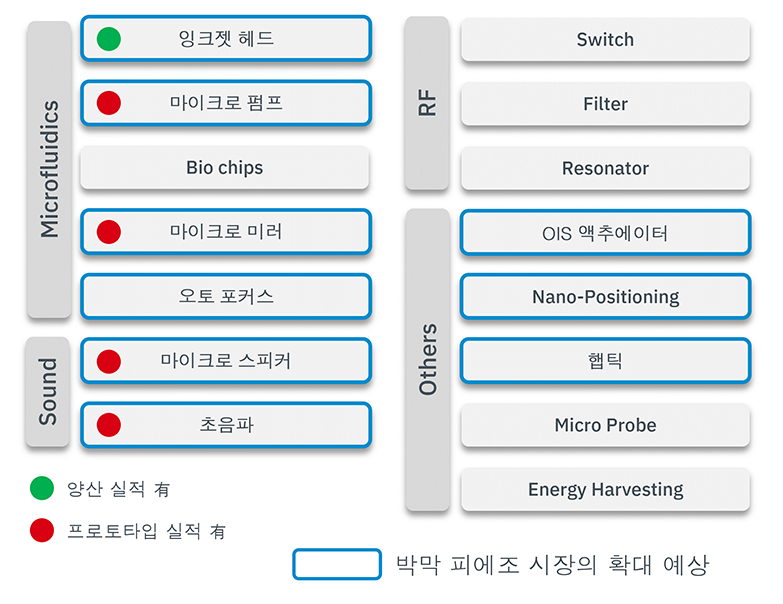

프로토타입 · 양산 실적 예

잉크젯 헤드에서의 양산 실적과 MEMS 기술의 연구를 통해 소형, 저전력, 높은 변위를 필요로 하는 액추에이터 디바이스를 고객과 공동으로 개발하여, 프로토타입 평가를 추진하고 있습니다.

프로세스 기술 예

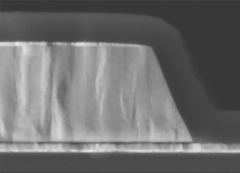

PZT 박막의 성능

【PZT stack 단면】

로옴은 1998년 세계 최초로 강유전체 메모리의 양산화에 성공하였습니다.

실리콘 웨이퍼에서의 PZT 박막 이용에 대해, 장기간에 걸쳐 축적한 경험과 노하우를 보유하고 있습니다.

로옴이 제공하는 Sol-gel PZT막은 자사에서 개발한 생산 설비에서 성막을 실시하여, 세계 최고 레벨의 압전 성능과 신뢰성을 실현합니다.

| 항목 | 수치 | 조건 |

|---|---|---|

| 압전 정수 : e31,f (-C/m2) | 19 | 10V/μm |

| 역압전 정수 : d31 (-pm/V) | 260 | 10V/μm |

| 절연 내압 (V/μm) | >75 | 실온, (평가 전원에 따른 제약) |

| 절연 수명 (년) | >10 | 20V/μm, 105℃, (가속 시험에 의한 추정) |

| 반복 수명 (회) | >1x1010 | 10V/μm, 변위 10% 감소 (단극 펄스) |

| 리크 전류 밀도 : (A/cm2) | <1x10-7 | 20V/μm |

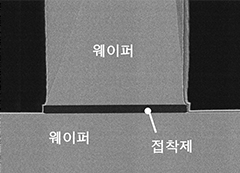

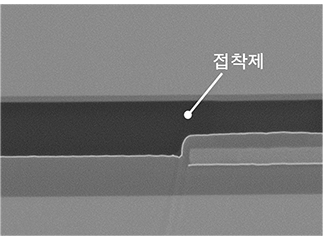

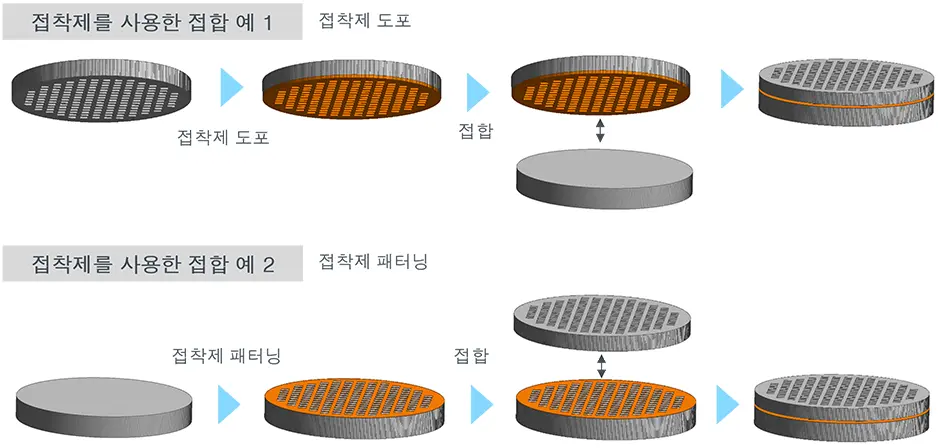

웨이퍼 레벨 접합 기술

【웨이퍼 접합 단면】

【웨이퍼 접합 단면 / 단차 상태】

여러 개의 실리콘 웨이퍼를 접합하는 기술을 보유하여, 복잡한 구조의 디바이스에서도 웨이퍼 레벨의 접합을 실시할 수 있습니다.

*접착제 도포 · 접합 프로세스 제안이 가능합니다.

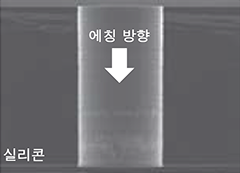

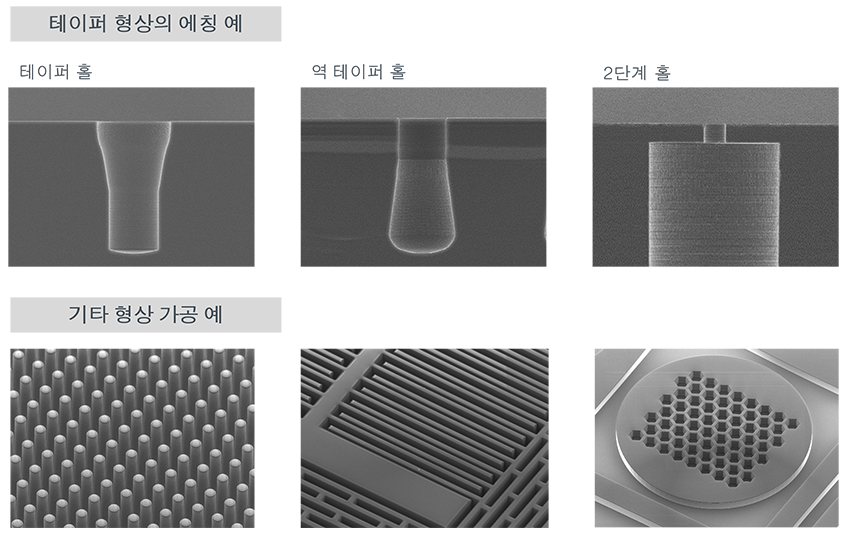

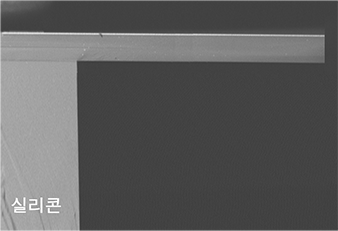

Si Deep RIE

【400μm Si 관통】

【실리콘 웨이퍼 가공】

자사 개발을 포함한 여러 회사의 Si Deep RIE 장치를 보유하여, 제품에 최적인 실리콘 에칭 프로세스 (형상, 공차, 이물질 레벨, 비용)를 제안합니다.

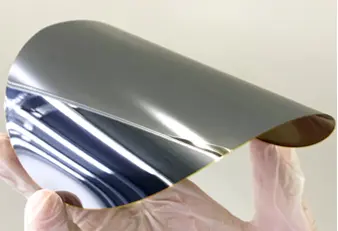

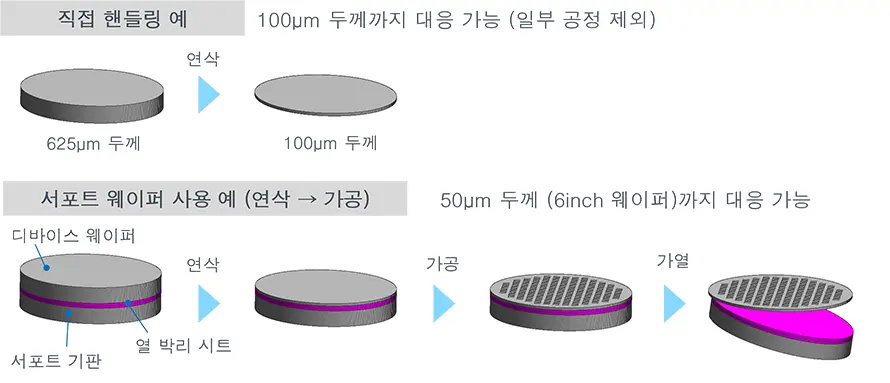

박형 웨이퍼 핸들링 기술

【얇은 실리콘 웨이퍼】

웨이퍼의 반송 설비를 자사에서 개발함으로써, 얇은 실리콘 웨이퍼의 프로세스 및 웨이퍼 접합을 가능하게 하였습니다.

【TAIKO 연삭 웨이퍼】

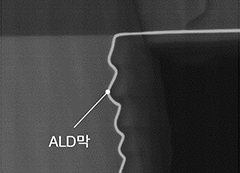

ALD 보호막 형성

【실리콘 형상 단면】

복잡한 凹凸 형상의 디바이스에서도, *ALD를 통해 균일하게 보호막을 형성할 수 있습니다.

*ALD:Atomic Layer Deposition (원자층 증착법)

보호막・・・외적 요인 (잉크, 접촉으로 인한 마모, 대전 등)으로부터 디바이스를 보호합니다.

ALD 성막의 자세한 설명 바로 가기 - 전자 기초 지식

압전 디바이스의 시뮬레이션 해석

【실리콘 캔틸레버 단면】

압전 디바이스의 유한 요소 시뮬레이션을 실시하여, 각종 디바이스에 대해 최적의 구조 및 프로세스를 제안할 수 있습니다.